英特爾剛剛宣布了其CPU設計的未來,將圍繞新的嵌入式多-DIE互連橋(EMIB)建造,這項技術將允許將不同世代的芯片縫合到同一包裝中。這也可能是AMD GPU Silicon進入了Intel處理器。

CPU和GPU性能是一回事,但是您的PC聽覺性能呢?查看我們的選擇最好的遊戲耳機今天附近。

報告PC世界從英特爾的技術和舊金山的製造日起,這種新的EMIB界面使新的異質CPU設計成為可能。根據英特爾的Murthy Renduchintala,這座新橋有望有大量的帶寬使不同的芯片能夠以“數百千兆字節”的速度相互交談。

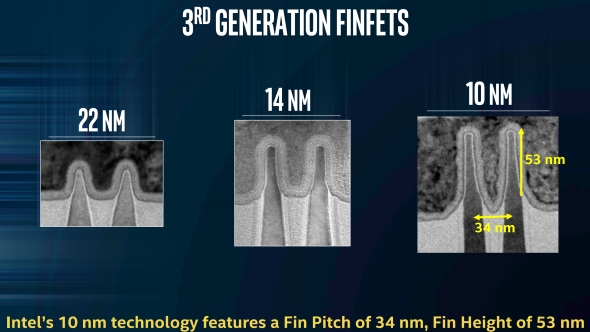

這種新的設計將意味著22nm,14nm和10nm矽都可以坐在同一處理器中,但是新的互連能夠將傳統的多芯片軟件包的傳統延遲降低四倍。

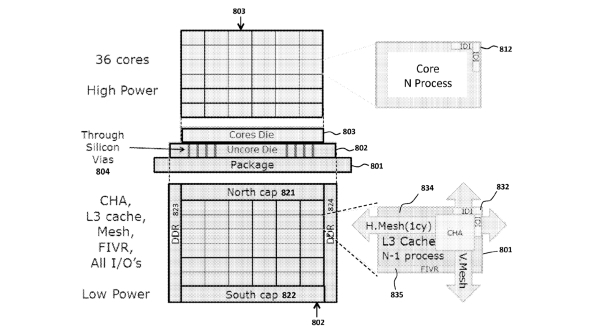

這個想法是為了使英特爾能夠迅速產生一代,而不必完全大修整個架構。然後,與不績效相關的組件可以保留在上一代的光刻上,而只有CPU設計的高性能部分才需要使用最新的下層流程節點。

這聽起來很糟糕專利申請Intel於2014年提交,最近通過尋求alpha。該專利涵蓋了將多個核心堆疊在一個包裝中的方法,並涵蓋了較小的3D堆疊設計的潛在成本降低,而不是較大的整體佈局,以及它至少將其減少到Intel Complect Server CPU的市場。它也有可能使英特爾也可以快速提高客戶處理器的核心計數。

不過,新的EMIB將取代矽插位器並通過矽VIA(TSV),並提供帶寬,從高性能的角度來實現此類設計。

它還為不同的矽設計以相互交流的速度鋪平了道路,以使他們成為大型整體設計的可行替代方案。這意味著,如果英特爾許可實際AMD GPU矽的謠言不僅是IP是真實的,這可能就是他們可以將Radeon芯片塞入英特爾包裝中的方式。

該專利說:“這種類似樂高的能力,可以合併大小核心,圖形,FPGA和自定義加速器,“提供了前所未有的靈活性,可以在彙編時間自定義服務器處理器,以適應特定的OEM工作負載和計算要求。”

英特爾沒有對這種“混合和匹配”異質設計何時進入生產做出任何承諾,但是據說Renduchintala在昨天的活動中提到了它將在近期Intel Products中發揮關鍵作用。

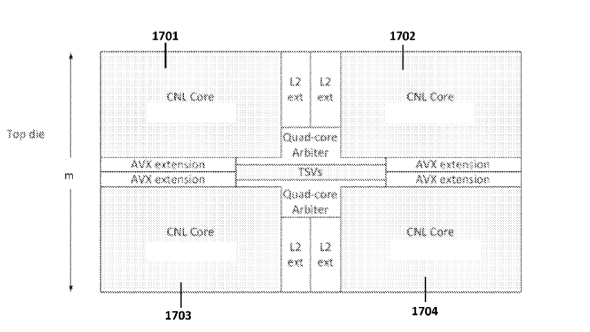

並使用專利申請詳細說明CNL(CannonLake)在其設計中,我們可以研究將即將到來的10nm移動設計進入更大,更高性能的處理器的方法。

CannonLake的10MN設計僅定為以低功率移動形式到達一年之交,這可能是由於早期光刻的產量低。通過使用這種異質設計,英特爾可以抵消10nm節點早期的較低產量,並且仍然在2018年晚些時候在10nm核心附近的高性能大砲CPU。